PLL Basic Topics - Cycle Slip

## What is the cycle slip?

PLL feedback clock normally will be increased or decreased the frequency to catch up with the reference clock.

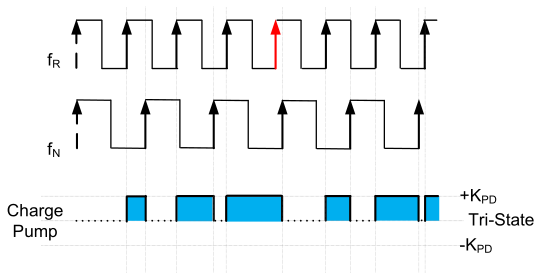

But when the feedback divider changed abruptly, it causes the one period of the feedback clock has two cycles of reference clock or one period of the reference clock has two cycles of feedback clock. The PFD output neglects one rising edge of reference clock or feedback clock. This is called cycle slip.

The slower frequency divider the frequency difference is the time of the first cycle slip. The difference is larger, the short time the cycle slip happens

## Why does it happen?

The above figure shows that one rising edge of reference clock is neglected by the PFD.

## What is the result? Is it bad for the PLL?

The PFD can recover, though, the cycle slip increase the lock time.

## How to determine the time of the first cycle slip?

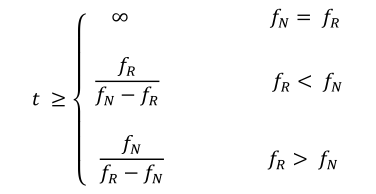

Assume the reference clock is fR, and divider frequency is fN.

If these two frequencies are different, the cycle slip will happen:

The slower frequency divided by the frequency difference is the time of the first cycle slip. The difference is larger, the short time the cycle slip happens

## Reference:

1. Banerjee, Dean. [**PLL Performance Simulation and Design Handbook, Fifth Edition**](https://www.ti.com.cn/cn/lit/ml/snaa106c/snaa106c.pdf), 2017. PDF

-

GDS file is the standard database file format. It is a binary file representing planar geometric shapes, text labels, and other information ...

-

markdown download the following zip file from official vim download page: https://www.vim.org/download.php **Runtime files** vim##rt.zip...

-

markdown 1. open file/close file/open terminal `:e` file_location\filename.txt `:clo` or `:close` close current p...